Puerta OR

| INPUT | OUTPUT | |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

La puerta OR o compuerta OR es una puerta lógica digital que implementa la disyunción lógica, se comporta de acuerdo a la tabla de verdad mostrada a la derecha. Cuando todas sus entradas están en 0 (cero) o en BAJA, su salida está en 0 o en BAJA, mientras que cuando al menos una o ambas entradas están en 1 o en ALTA, su SALIDA va a estar en 1 o en ALTA. En otro sentido, la función de la compuerta OR efectivamente encuentra el máximo entre dos dígitos binarios, así como la función AND encuentra el mínimo.[1]

Se puede ver claramente que la salida X solamente es "0" (0 lógico, nivel bajo) cuando la entrada A como la entrada B están en "0". En otras palabras la salida X es igual a 0 cuando la entrada A y la entrada B son 0.

La expresión matemática es: Output = a+b

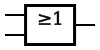

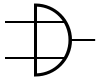

Símbolos

Hay tres símbolos para las puertas OR: el símbolo Americano (ANSI o "militar") y el símbolo IEC ("europeo" o "rectangular"), así como el obsoleto símbolo DIN.[2][3] Para obtener más información, véase Puerta lógica.

|  |  |

| Símbolo ANSI o "Militar" | Símbolo IEC | Símbolo DIN |

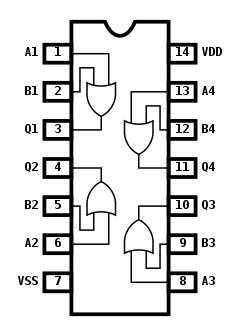

Descripción del hardware y configuración de pines

Las puertas OR son puertas lógicas básicas, y como tales están disponibles en TTL y familias lógicas de CI CMOS. La serie estándar 4000 de los CI CMOS es el 4071, que incluye cuatro puertas OR independientes de dos entradas. La versión tradicional TTL es el 7432. Existen muchas ramas de la puerta OR 7432 original. Todas tienen el mismo pinout pero diferente arquitectura interna, que les permite operar en diferentes rangos de voltaje y/o a velocidades más altas. En adición a la puerta OR estándar de 2-entradas, también están disponibles puertas OR de 3 y 4 entradas. En la serie CMOS, estas son:

- 4075: Puerta OR triple de 3 entradas

- 4072: Puerta OR dual de 4 entradas

Las variaciones TTL incluyen:

- 74LS32: Puerta OR cuádruple de 2 entradas (de baja potencia versión Schottky)

- 74HC32: Puerta OR cuádruple de 2 entradas (versión CMOS de alta velocidad) - tiene menor consumo de corriente / mayor rango de voltaje

- 74LVC32: Versión CMOS de bajo voltaje de la misma.

Descripción del lenguaje hardware

módulo (a, b, c); de entrada a, b; c salida; o (c, a, b); fin;

Implementaciones

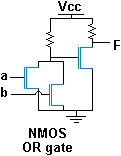

|  |  |  |

Alternativas

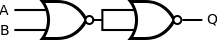

En caso de no estar disponibles puertas OR específicas, se puede hacer de NAND o NOT en la configuración que se muestra en la imagen a la derecha de este texto. Cualquier puerta lógica se puede hacer a partir de una combinación de puertas NOR o NAND.

| Construcción de NAND | Construcción de NOR |

|---|---|

|  |

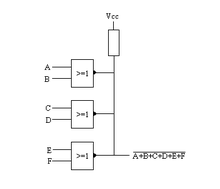

OR cableado

Con el colector abierto bajo activo, tal como se utiliza para señales de control en muchos circuitos, una función OR puede ser producida por el cableado junto con varias salidas. Este arreglo se llama OR cableado. Esta implementación de una función OR también se encuentra típicamente en los circuitos integrados de N o en los procesos de transistor solo de tipo P.

Véase también

Wikimedia Commons alberga una categoría multimedia sobre Puerta OR.

Wikimedia Commons alberga una categoría multimedia sobre Puerta OR.

- Puerta AND

- Puerta NOT

- Puerta NAND

- Puerta NOR

- Puerta XOR

- Puerta XNOR

- Álgebra de Boole

- Puerta lógica

Referencias

- ↑ «OR Gate» (en inglés). Hyperphysics.phy-astr.gsu.edu. Consultado el 24 de septiembre de 2012.

- ↑ Harris, David Harris, Sarah (2007). Digital design and computer architecture (1era edición). San Francisco, Calif.: Morgan Kaufmann. pp. 21. ISBN 9780123704979.

- ↑ Brumbach, Michael E. (2011). Industrial electricity (en inglés) (8va edición). Clifton Park, N.Y.: Delmar. pp. 546. ISBN 9781435483743.

Enlaces externos

- «Tecnología de las computadoras, Prof. Ing. Mauricio Vistosi». blogspot.com. Consultado el 24 de agosto de 2014.

- «Web sobre Arquitectura de Computadores y Electrónica Digital». vistosi.com.ar. Archivado desde el original el 1 de julio de 2014. Consultado el 24 de agosto de 2014.

- Esta obra contiene una traducción total derivada de «OR gate» de Wikipedia en inglés, concretamente de esta versión, publicada por sus editores bajo la Licencia de documentación libre de GNU y la Licencia Creative Commons Atribución-CompartirIgual 4.0 Internacional.

Datos: Q560398

Datos: Q560398 Multimedia: OR gates / Q560398

Multimedia: OR gates / Q560398