Intel 4004

| |

| 生産時期 | 1971年11月15日から1981年まで |

|---|---|

| 生産者 | Intel |

| CPU周波数 | 740 kHz から 750 kHz |

| 命令セット | 4-bit BCD oriented |

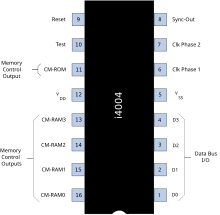

| パッケージ | 16 pin DIP |

| 次世代プロセッサ | Intel 4040 |

| トランジスタ | 2250 |

| テンプレートを表示 | |

4004(よんまるまるよん、と読まれることが多い)は、日本のビジコンと米国のインテルによって共同開発された、民生用としては世界初の1チップのマイクロプロセッサ[1]であり、軍用のMP944[2]とほぼ同時期の、世界最初期のマイクロプロセッサのひとつである。周辺ファミリICを含めてMCS-4 Micro Computer Set、あるいは略し単にMCS-4とも呼ぶ。

1971年発表、4ビットマイクロプロセッサである。クロック周波数は、500kHzから741kHz[3]である。回路構成はクロック同期設計で、pMOSプロセスで3mm×4mmのチップ(ダイ)の上に2,300個のトランジスタを集積、10µm (0.01mm) ピッチのプロセス・ルールで製造された。当時のICとして標準的な16ピンDIPのパッケージに収納するため、物理的に4ビット幅のバスを、アドレスとデータで時分割で使用している。

歴史

1969年、ビジコンはプログラム制御[5]の電卓を計画し、インテルにそのためのチップセットの開発を依頼していた。ビジコンの当初案では、マクロ命令による制御で、10個前後[6][7]のチップが必要というものだった。これは電卓としては汎用(プログラム次第でいろいろな電卓ができる)だが、電卓用という意味では専用のチップ、というものであった。

これに対し、当時のインテルの規模ではそれだけ多くの種類のチップを同時に開発するのは手に余るため、インテルの技術者テッド・ホフは、ワード長が4ビットであることを除けば、汎用のコンピュータそのものという構成を提案した。複数桁の演算処理は、1桁(4ビット)の演算の反復で置き換えればよく、また、外部機器の制御も、ソフトウェアによる制御に置き換えればよい、というのである。これにより開発するチップの種類を削減した。1969年8月末のことで、マイクロプロセッサの原点となった。

このアイディアにもとづき、嶋正利とフェデリコ・ファジンが中心となって、嶋が論理設計しファジンが物理設計(回路設計とマスクレイアウト)を行い、4004は完成した。もともとの開発日程では、1970年7月から10月にかけて、4001から4004までが量産されるはずであったが、ファジンが配属になった初日に日程を見た彼は「あごが落ちた(びっくりした、の意)」とされ(CPUを含む4つのチップの設計期間が6カ月もなかった)、そのすぐ後に進捗確認のため渡米した嶋が開発の遅れを知って激怒し、(intelがより多くのエンジニアを雇う一方で)嶋がそのまま6ヶ月設計に携わった結果である[8]。

当初の契約では、このチップはビジコンに対する専売となっていたが、チップの汎用性に気付いたインテルが他への販売を希望し、一方でビジコン側は会社の運転用のつなぎ資金の要求が常にあった事から、契約金の一部をビジコンに払い戻すことでインテルはチップの販売権を得て、1971年11月15日に4004として出荷が開始された。

特徴

- 最高動作周波数 741kHz。ただし、命令アドレス出力に3クロック、命令読み出しに2クロック、命令実行に3クロックの計8クロックを要する。

- プログラムのメモリ空間とデータのメモリ空間の分離(ハーバード・アーキテクチャ)。近年のキャッシュのそれのような性能目的による物理的なバスの分離ではなく、命令セットアーキテクチャ的(論理的)にそれぞれの空間が異なる、というものである。

- また、ピン数の節約のため、以下の信号は単一の4ビット物理バスを共用(時分割多重化)し、またデータ以外はそれぞれ順次送り出す方式である。

- 12ビットのアドレス

- 8ビットの命令

- 4ビットのデータ

- 46種の命令がある(うち41種は8ビット長、5種は16ビット長)[9][10][11][12]。

- 16個の4ビット長レジスタ

- RAMのアドレスを指すようなスタックポインタは無く、プログラムカウンタ直結の、サブルーチン呼出時の退避専用のハードウェアスタックがある。深さは3段。

MCS-4

当初の周辺チップとしては、容量2048bitのマスクROM 4001、容量320bitのRAM 4002、10bitシフトレジスタ兼10bit出力ポートの4003があった。これらを含めてMCS-4(Micro Computer Set)とした。

初期ファミリ内でのチップの組み合わせで、ROM 32768bit(2048bit×16)、RAM 1280bit(320bit×4)の構成が可能。

ビジコンの目的であった電卓における構成は、だいたい以下のようなものとなる。

- 4001に関数などのプログラムが格納されている

- 4003でキー入力をシフトしながら4004へ渡す

- 4004で入力された数値を4002に書き込む

- 4001にあるプログラムを使って4004で1桁ずつ演算を行い結果を4002に書き込む

- 4003でシフトしながら表示板に出力する

脚注

- ^ 日経クロステック(xTECH). “世界初のCPU「4004」開発回顧録”. 日経クロステック(xTECH). 2022年1月5日閲覧。

- ^ F-14戦闘機用Central Air Data Computer

- ^ Datasheet Intel 4004 (PDF) より:クロック周期最小1.35µsec(約741kHz)/最大2.0µsec(500kHz)。『マイクロコンピュータの誕生』によれば、先に周波数を750kHzと決め、そこからその周期内で動作するよう機能を決めている

- ^ 国立科学博物館

- ^ 『電子立国日本の自叙伝』第5回「8ミリ角のコンピューター」ではこれを「ストアードプログラム」と説明しているが、普通のコンピュータのような汎用という訳ではない。また嶋は著書で「ランダム論理」(ワイヤード論理制御)に対するものとして「プログラム論理」という語を使っている。

- ^ 嶋の著書『マイクロコンピュータの誕生』によれば、何回か提案しており数は上下する。インテルは12種類としている。嶋は最終的にはプリンタ付きで8個、表示のみで6個まで削減できたと書いている(同著39頁)。

- ^ 嶋 正利『マイクロコンピュータの誕生』岩波書店、1987年8月28日、50-51頁。ISBN 4-00-006021-X。

- ^ Cass, Stephan (2021). “Intel's 4004 Turns 50”. IEEE Spectrum 58 (11): 9-10.

- ^ “4004 SINGLE CHIP 4-BIT P-CHANNEL MICROPROCESSOR”. www.applelogic.org. 2022年1月5日閲覧。

- ^ “4004 SINGLE CHIP 4-BIT P-CHANNEL MICROPROCESSOR”. datasheets.chipdb.org. 2022年1月5日閲覧。

- ^ “MCS-4 Assembly Language Programming Manual PRELIMINARY EDITION”. bitsavers.trailing-edge.com. 2022年1月5日閲覧。

- ^ “MCS-4 FOUR-BIT PARALLEL MICRO COMPUTER SET”. codeabbey.github.io. 2022年1月5日閲覧。

参考文献

- 嶋正利『マイクロコンピュータの誕生 : わが青春の4004』岩波書店、1987年。doi:10.11501/12629869。https://dl.ndl.go.jp/ja/pid/12629869/1/4。

関連項目

外部リンク

- インテル博物館

- 嶋正利氏の4004開発回顧録

- 4004 Dr嶋 ブログ | Visual Technology Premier Site - ウェイバックマシン(2006年1月6日アーカイブ分)

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 生産終了 |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 現行 |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| その他 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| マイクロ アーキテクチャ |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||